AI가 칩을 설계한다는 발상

안드레이 카파시(Andrej Karpathy)가 제안한 "LLM 진화 루프"라는 아이디어가 있어요. 이게 뭐냐면, 거대언어모델한테 어떤 결과물을 만들게 하고, 그걸 평가해서 점수를 매긴 다음, 더 잘하는 방향으로 다시 만들게 하는 걸 반복하는 거예요. 일종의 자연선택을 AI에게 시키는 거죠. FeSens라는 분이 이 루프를 CPU 아키텍처 설계에 돌려본 실험을 공개했는데, 이름이 "Auto-Architecture Tournament"예요.

어떻게 동작하는지

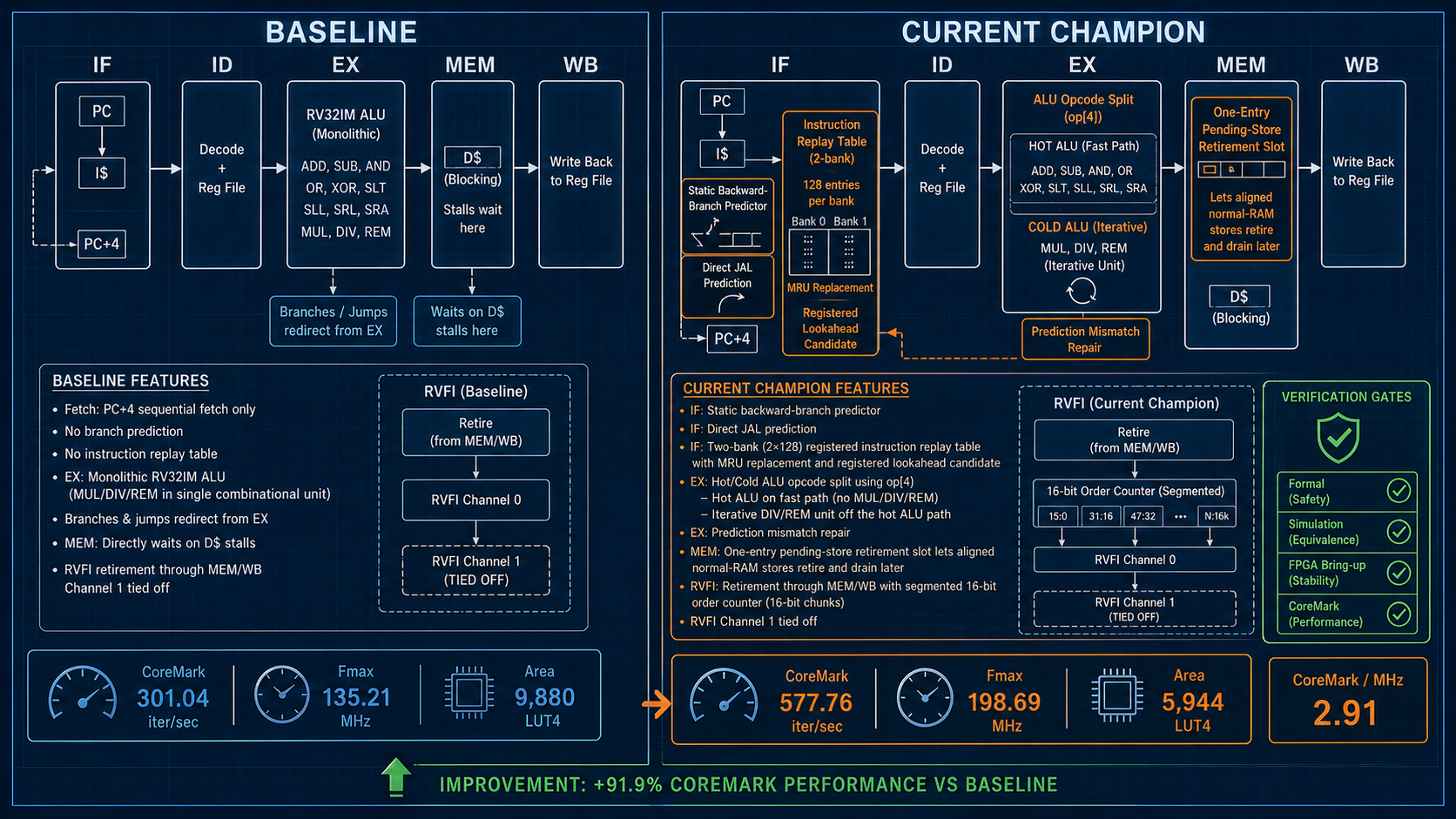

실험의 골자는 이래요. LLM에게 "이런 명령어 셋(ISA)과 마이크로아키텍처를 가진 CPU를 설계해봐"라고 시킵니다. 그러면 모델이 Verilog 같은 하드웨어 기술 언어로 설계를 토해내고, 시뮬레이터에서 벤치마크를 돌려요. 단순한 정렬이나 행렬 곱셈 같은 작업을 시켜서 사이클 수, 전력 효율, 게이트 카운트 같은 메트릭을 측정하는 거죠. 그 결과를 다시 모델한테 "네가 만든 설계는 이런 점수를 받았어. 더 나은 걸 만들어봐" 하고 피드백으로 넣어주면, 모델이 다음 라운드에서 개선된 설계를 내놓는 식이에요.

토너먼트라는 이름이 붙은 이유는, 여러 후보 설계를 동시에 만들고 서로 경쟁시켜서 살아남는 설계만 다음 라운드로 보내기 때문이에요. 진화 알고리즘에서 말하는 선택압을 그대로 적용한 거죠. 라운드를 거듭할수록 설계가 점점 정교해지고, 처음엔 그냥 동작도 안 하던 회로가 나중엔 꽤 그럴듯한 파이프라인 구조까지 갖추게 되는 과정이 흥미로워요.

기술적 디테일

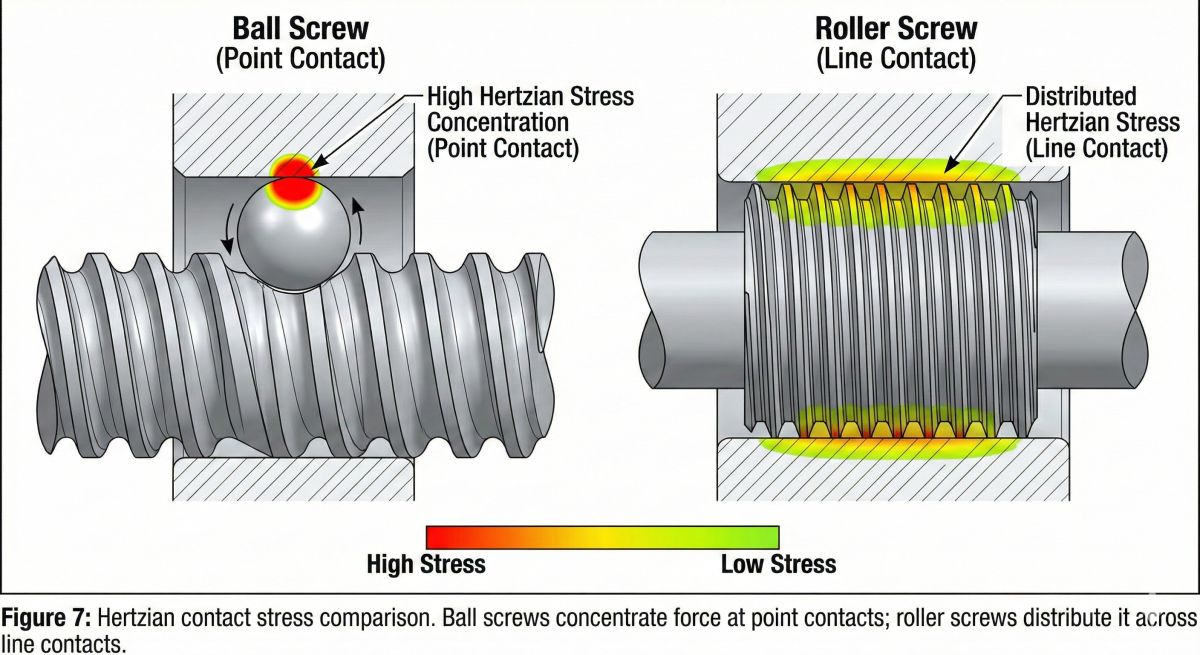

Verilog 코드를 LLM이 직접 생성하면 합성(synthesis) 단계에서 오류가 잔뜩 나기 때문에, 이 프로젝트에서는 검증과 시뮬레이션을 자동화한 파이프라인을 구축했어요. 설계가 컴파일도 안 되면 0점을 주고 탈락시키고, 동작은 하지만 비효율적이면 낮은 점수를 주는 식이에요. 평가 메트릭으로는 IPC(클럭당 명령어 수), 면적 효율, 전력당 성능 같은 전통적인 칩 설계 지표를 씁니다.

흥미로운 점은, 모델이 사람이 알고 있는 최적화 기법(파이프라이닝, 분기 예측, 캐시 계층 같은 것들)을 "발견"해 나간다는 거예요. 처음엔 단순한 단일 사이클 CPU를 만들다가, 점수를 더 받기 위해 스스로 파이프라인을 도입하고, 해저드 처리를 추가하는 모습이 관찰됐대요. 물론 사람 손으로 다듬은 상용 CPU에 비할 바는 못 되지만, 자동화된 탐색만으로 어디까지 갈 수 있는지를 보여주는 의미 있는 실험이에요.

업계 맥락에서 보면

이런 시도가 처음은 아니에요. 구글이 AlphaChip으로 칩 플로어플래닝을 강화학습으로 푼 사례도 있고, MIT에서 LLM으로 RTL 코드를 생성하는 연구도 있었거든요. 다만 이번 실험은 "끝에서 끝까지(end-to-end)" 루프를 단순한 평가 함수와 함께 돌렸다는 점에서 접근법이 단순하고 재현하기 쉽다는 장점이 있어요. 카파시가 말한 진화적 코드 생성 패러다임이 단순 소프트웨어를 넘어 하드웨어까지 확장될 수 있다는 가능성을 보여주는 거죠.

한국 개발자에게 주는 시사점

반도체 강국인 우리나라에서 이런 자동 설계 패러다임은 결코 남의 이야기가 아니에요. 당장 상용 칩을 LLM이 설계하긴 어렵겠지만, 작은 가속기나 도메인 특화 프로세서(DSA)를 빠르게 프로토타이핑할 때는 충분히 활용 가치가 있어요. 또 LLM을 도구로 쓰는 "평가 가능한 루프"를 만드는 노하우는 칩 설계뿐 아니라 컴파일러 최적화, 알고리즘 탐색, 인프라 자동화 등 다양한 영역에 응용할 수 있어요. 결국 핵심은 모델이 점수를 받고 개선할 수 있는 명확한 평가 함수를 어떻게 만드느냐예요.

여러분이라면 어떤 영역에 이런 진화 루프를 적용해보고 싶으세요? 그리고 평가 함수가 빠지면 이런 접근이 작동할 수 있을까요?

🔗 출처: Hacker News

"비전공 직장인인데 반년 만에 수익 파이프라인을 여러 개 만들었습니다"

실제 수강생 후기- 비전공자도 6개월이면 첫 수익

- 20년 경력 개발자 직강

- 자동화 프로그램 + 소스코드 제공